提供軟硬件一體解決方案,「睿思芯科」打造高性能、低功耗RISC

RISC-V架構(gòu)具有設(shè)計簡單、完全開源、模塊化等極其符合現(xiàn)代小型化計算設(shè)備需求的特點,其誕生于美國加州大學柏克萊分校,在此后的數(shù)年里迅速成長。在X86架構(gòu)和ARM架構(gòu)指令集冗雜、商業(yè)授權(quán)成本無比昂貴的情況下,RISC-V架構(gòu)已經(jīng)成為了未來小型智能硬件設(shè)備的絕好選擇。

如今,我國AIoT產(chǎn)業(yè)蓬勃發(fā)展,智能物聯(lián)網(wǎng)設(shè)備越來越追求低功耗、運算快、能順利完成某一項或某幾項計算任務。在這種需求下,企業(yè)不愿意通過支付高昂的授權(quán)費而去研發(fā)一個大而全的,但能耗高、體積大的芯片,相反,芯片擁有簡潔的設(shè)計,能夠滿足具體設(shè)備的定制化需求才是企業(yè)和市場所關(guān)心的。

而這也是而睿思芯科(深圳)技術(shù)有限公司注重于研發(fā)RISC-V架構(gòu)的處理器芯片,為企業(yè)提供完整的RISC-V解決方案的初衷。

睿思芯科成立于2018年8月,是一家基于RISC-V架構(gòu),為智能網(wǎng)聯(lián)生態(tài)提供核心處理器的芯片公司。創(chuàng)始團隊來自加州伯克利大學RISC-V原創(chuàng)項目組,具備RISC-V和AI芯片領(lǐng)域的深厚學識和卓越研發(fā)實力。睿思芯科的創(chuàng)始人譚章熹告訴創(chuàng)業(yè)邦:“我們早在2017年就預測到了國內(nèi)市場對RISC-V架構(gòu)處理器的需求。”

譚章熹在清華大學電子工程系獲得學士和碩士學歷后前往加州大學伯克利分校深造,師從圖靈獎得主David Patterson,取得了計算機科學博士學位,由于RISC-V架構(gòu)就出自David Patterson之手,這意味著譚章熹博士成了離RISC-V技術(shù)最近的中國人。

從2018年開始,國內(nèi)大量的RISC-V企業(yè)相繼出現(xiàn)。其中有一部分企業(yè)用不同的架構(gòu)進行混合開發(fā),或是專注于ASIC芯片,還有一部分企業(yè)致力于RISC-V架構(gòu)處理器的IP設(shè)計,方向各異。

從表面上來看,RISC-V架構(gòu)的完全開源、完全免費的屬性似乎成為了其迅速發(fā)展的重要因素,但從本質(zhì)上來說,RISC-V架構(gòu)更像是一種新的通用開放標準,在這種標準下開發(fā)者可以通過一套架構(gòu)滿足不同的運算需求,這種定制化的能力是RISC-V架構(gòu)真正的優(yōu)勢。譚章熹表示“RISC-V架構(gòu)并不是ARM架構(gòu)的廉價替代,而是要完成ARM架構(gòu)完成不了的任務。”

正因如此,譚章熹從創(chuàng)業(yè)之初就瞄準了基于RISC-V架構(gòu)的處理器研發(fā),在譚章熹看來,企業(yè)應該在RISC-V生態(tài)上做出具有完整落地能力的芯片才能真正滿足市場上的AIoT設(shè)備的需求,其中具體的軟硬件一體設(shè)計、系統(tǒng)優(yōu)化、封裝優(yōu)化等技術(shù)是簡單的架構(gòu)IP設(shè)計所不能達到的。

睿思芯科核心成員進行技術(shù)討論

目前,睿思芯科已經(jīng)完成了兩款SoC芯片的研發(fā),其中Pygmy是一款面向特定領(lǐng)域的人工智能的芯片,擁有4個可編程AI加速引擎,支持GCC編譯器和Linux系統(tǒng)。

利用獨有的特定領(lǐng)域架構(gòu),Pygmy可針對用戶特殊的垂直應用需求自由組合相應的指令集模塊,在CPU層面進行裁剪,并能夠?qū)⒏咝阅艿?AI 算力注入到低功耗的物聯(lián)網(wǎng)終端的各類AI應用中,例如智能家居的人機交互、安防監(jiān)控的圖像識別、無人駕駛的傳感器融合等場景。

而Pygmy-E芯片則基于模塊化設(shè)計方法,屬于Pygmy架構(gòu)下的一個低功耗單元單獨形成的MCU產(chǎn)品。Pygmy-E能夠高效運行RTOS等物聯(lián)網(wǎng)操作系統(tǒng),采用了1.8V低電壓設(shè)計,支持高主頻運行,并在Pygmy的基礎(chǔ)上實現(xiàn)了更的高性能和更的低功耗。Pygmy-E芯片適用于AI+物聯(lián)網(wǎng)終端,性能功耗對標ARM cortex M series系列的MCU有明顯優(yōu)勢,Pygmy-E的功耗是其7%,Core Mark性能得分是其1.2倍。

目前睿思芯科的兩款芯片均采用28nm制程。譚章熹表示,其芯片的低功耗主要來源于其自主設(shè)計的ORV32位內(nèi)核的CPU架構(gòu),這種底層設(shè)計能力使得睿思芯科的產(chǎn)品即使沒有采用更高的制程,但仍然有著極其優(yōu)秀的性能。

這一方面可以更好地使產(chǎn)品落地并迅速應用到智能產(chǎn)品中,另一方面也提高了目前國產(chǎn)芯片制程有待提高的特殊時期內(nèi)的企業(yè)抗風險能力。“無論是從技術(shù)的角度還是經(jīng)濟的角度,我們都不能一味地追求利用制程來提升芯片的性能。”譚章熹對創(chuàng)業(yè)邦說道。

硬件上,睿思芯科做到了CPU設(shè)計、芯片的封裝生產(chǎn);軟件上其可以支持市面上已經(jīng)成熟的大多數(shù)商業(yè)操作系統(tǒng),這種軟硬件一體化的解決方案讓睿思芯科獲得了極大的市場優(yōu)勢。

據(jù)了解,睿思芯科的具體合作的客戶正在逐步累積。人員方面,睿思芯科的核心團隊成員多數(shù)擁有名校背景,且具有多年相關(guān)領(lǐng)域的豐富實踐經(jīng)驗。

融資方面,睿思芯科于2019年完成了由翼樸資本、力合創(chuàng)投及百度風投投資的天使輪融資,融資資金主要用于產(chǎn)品落地和技術(shù)研發(fā),據(jù)了解,睿思芯科新一輪的融資也在計劃中。

本文文章圖片來源于睿思芯科,經(jīng)授權(quán)使用。本文為創(chuàng)業(yè)邦原創(chuàng),未經(jīng)授權(quán)不得轉(zhuǎn)載,否則創(chuàng)業(yè)邦將保留向其追究法律責任的權(quán)利。如需轉(zhuǎn)載或有任何疑問,請聯(lián)系editor@cyzone.cn。

關(guān)鍵詞: 提供軟硬件一體解決方

責任編輯:hnmd003

相關(guān)閱讀

-

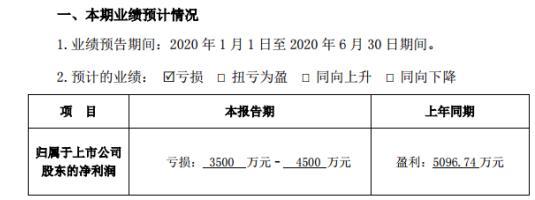

金固股份:2020年預計虧損3500萬元–4500萬元

7月14日消息,金固股份(002488)發(fā)布2020年半年度業(yè)績預告:去年預計虧損3500萬元–4500萬元,上年...

2020-07-27 -

成都路橋(002628)急速拉升0.18元,漲幅4.43%

2020年07月08日,成都路橋(002628)急速拉升0 18元,漲幅4 43%,成交量1492 93萬股,成交額6155 53萬...

2020-07-23 -

7月17日招商中證白酒指數(shù)分級公布最新凈值,下跌8.69%

7月17日招商中證白酒指數(shù)分級證券投資基金(簡稱:招商中證白酒指數(shù)分級,代碼161725)公布最新凈值,下跌...

2020-07-22 -

07月21日富國創(chuàng)業(yè)板B上漲5.40%,成交17005.69萬元

07月21日富國創(chuàng)業(yè)板B上漲5 40%,成交17005 69萬元。截至目前場內(nèi)價格為1 639元, 當前本基金場外凈...

2020-07-21 -

A股快報 | 地產(chǎn)板塊上漲1.38% 金科股份上漲10.04%

觀點網(wǎng)訊:1月20日,滬深股市開盤后(9時36分),地產(chǎn)行業(yè)32只股票(觀點指數(shù)監(jiān)測的樣本企業(yè))22只上漲...

-

長沙雨花城投集團20億公司債項目狀態(tài)更新為“已反饋”

觀點網(wǎng)訊:1月20日,據(jù)上交所公司債券項目信息平臺披露,長沙市雨花城市建設(shè)投資集團有限公司2021年面向...

-

國金證券趙偉:MLF和LPR下調(diào),或并非新一輪貨幣寬松周期的終點

國金證券首席經(jīng)濟學家趙偉20日表示,1年LPR下調(diào)10BP、5年LPR下調(diào)5BP,基本符合市場預期。5年LPR下調(diào)并不...

-

上海:去年籌建保障性租賃住房6.7萬套 房地產(chǎn)市場平穩(wěn)健康發(fā)展

觀點網(wǎng)訊:1月20日,上海市第十五屆人大六次會議在世博中心開幕,上海市市長龔正作《政府工作報告》。龔...

-

中國奧園:將不支付2022年1月票據(jù)余下本金

焦點財經(jīng)訊盼盼1月20日,中國奧園(3883 HK)發(fā)布公告稱,截至2021年12月31日止年度,中國奧園集團錄得...

-

嚴躍進:5年期以上LPR下調(diào)5BP,100萬貸款金額30年期等額本息每月少還30元

金融界1月20日消息央行下調(diào)兩大政策利率后,1月LPR報價利率也跟隨下調(diào)。據(jù)中國人民銀行授權(quán)全國銀行間同...

-

湯加海底火山噴發(fā)未對我國遠洋漁業(yè)捕撈造成直接影響

記者昨天從農(nóng)業(yè)農(nóng)村部了解到,這次湯加海底火山大范圍噴發(fā),未對我國遠洋漁業(yè)捕撈造成直接影響。 遠...

-

寧夏科技創(chuàng)新破解產(chǎn)業(yè)發(fā)展瓶頸

2021年,自治區(qū)科技廳緊緊圍繞全區(qū)重點產(chǎn)業(yè)轉(zhuǎn)型發(fā)展需求,加強科技攻關(guān)和成果轉(zhuǎn)化,著力破解產(chǎn)業(yè)發(fā)展的...

-

港股快報 | 物業(yè)板塊普漲 碧桂園服務現(xiàn)時領(lǐng)漲13.64%

觀點網(wǎng)訊:1月20日,經(jīng)過港交所盤前集中競價,51只H股物業(yè)股中9只低開,26只高開,其中碧桂園服務開盤漲...

-

國內(nèi)期市開盤漲多跌少 滬鎳主力合約漲近5%

上證報中國證券網(wǎng)訊1月20日,國內(nèi)期市日間盤開盤漲多跌少,截至9時05分,滬鎳主力合約漲近5%,滬錫、菜...

-

或因降息地產(chǎn)股債均現(xiàn)大幅上漲 融創(chuàng)中國漲超8%、佳兆業(yè)超6%

觀點網(wǎng)訊:1月20日,港股融創(chuàng)中國漲超8%,世茂集團漲超7%,佳兆業(yè)集團漲超6%。A股華遠地產(chǎn)漲停,新城控...

-

北京市奧林匹克專用車道21日啟用

根據(jù)北京市交管部門《關(guān)于北京2022年冬奧會和冬殘奧會期間北京市設(shè)置奧林匹克專用車道有關(guān)事項的通告》...

-

禹洲集團4.77億美元票據(jù)獲得展期

焦點財經(jīng)訊盼盼1月20日,禹洲集團發(fā)布公告稱,其已成功獲得絕大多數(shù)交換票據(jù)持有人的支持,及所有征求同...

-

馬云與蔡崇信以1.88億美元購入美國紐約一個復式豪宅

觀點網(wǎng)訊:1月20日,阿里巴巴創(chuàng)辦人馬云與執(zhí)行副主席蔡崇信共同持有的BluePoolCapital,以1 88億美元購...

-

五項新國標發(fā)布 推動非常規(guī)水源安全高效利用

國家市場監(jiān)管總局(標準委)日前批準發(fā)布了《水回用導則再生水廠水質(zhì)管理》等5項污水資源化領(lǐng)域推薦性國...

-

黃河流域“清廢行動”取得階段性成果 今年將有序推進陜晉豫魯四省行動開展

記者近日從生態(tài)環(huán)境部獲悉:2021年黃河流域“清廢行動”立查立改點位全部完成整治。各地累計投入資金240...

-

李宇嘉解讀LPR非對稱降息:傳達穩(wěn)定但不刺激的信號,一季度樓市或開始觸底

廣東省住房政策研究中心首席研究員李宇嘉表示,上一次調(diào)降5年期LPR還是2020年4月的事,這也是20個月來首...

-

我國光纖量子密鑰分發(fā)距離創(chuàng)世界紀錄

中國科學技術(shù)大學郭光燦院士團隊韓正甫教授及其合作者王雙、銀振強、何德勇、陳巍等,近期實現(xiàn)833公里光...

-

華發(fā)投資控股50億小公募獲深交所通過

觀點網(wǎng)訊:深交所1月19日信息披露,珠海華發(fā)投資控股集團有限公司2021年面向?qū)I(yè)投資者公開發(fā)行公司債券...

-

?港交所CEO歐冠升:中國內(nèi)地資本市場規(guī)模10年后將超過100萬億美元

觀點網(wǎng)訊:香港交易所集團行政總裁歐冠升1月19日在其網(wǎng)志中預測,未來10年國內(nèi)地資本市場的廣度和深度都...

-

長三角示范區(qū)推動跨域公共數(shù)據(jù)“無差別”共享共用

記者近日從長三角生態(tài)綠色一體化發(fā)展示范區(qū)執(zhí)委會獲悉:示范區(qū)執(zhí)委會與上海市大數(shù)據(jù)中心、江蘇省大數(shù)據(jù)...

-

2021年長江六座梯級水電站累計發(fā)電2628.83億千瓦時 當前儲能約210億千瓦時

記者從中國長江三峽集團有限公司獲悉:截至2021年12月31日,長江干流葛洲壩、三峽、向家壩、溪洛渡、白...

-

5年期LPR下調(diào)5bp!20個月首次!房貸利率將迎全面下調(diào) 業(yè)內(nèi)預計降準降息政策調(diào)整空間仍存

5年期LPR下調(diào)5bp!20個月首次!房貸利率將迎全面下調(diào)業(yè)內(nèi)預計降準降息政策調(diào)整空間仍存業(yè)內(nèi)人士認為,目...

-

國家糧食和物資儲備局部署2022年春節(jié)、“兩會”及冬奧會、冬殘奧會期間糧油市場保供穩(wěn)價工作

上證報中國證券網(wǎng)訊據(jù)國家糧食和物資儲備局1月20日消息,近日,國家糧食和物資儲備局召開2022年春節(jié)、“...

-

廣州期貨交易所與德意志交易所集團簽署諒解備忘錄 探索綠色金融領(lǐng)域的國際合作

上證報中國證券網(wǎng)訊(記者朱文彬)據(jù)廣州期貨交易所(簡稱“廣期所”)消息,該所與德意志交易所集團(...

-

網(wǎng)上逛花市 天貓超市把200多種年宵花搬上網(wǎng)“現(xiàn)摘現(xiàn)發(fā)”

還有不到一周就是小年,逛逛紅火的花市,買份年宵花為新春“錦上添花”,是年味兒必不可少的組成部分。...

-

新冠檢測新分支!冬奧會將使用氣溶膠新冠病毒檢測系統(tǒng)

近日,清華大學、北京大學、中國醫(yī)學科學院病原生物學研究所、昌平實驗室等科研人員聯(lián)合研制出公共空間...

-

紐約金價19日上漲

新華社芝加哥1月19日電(記者徐靜)紐約商品交易所黃金期貨市場交投最活躍的2月黃金期價19日比前一交易...

-

這一大宗商品價格創(chuàng)逾7年新高 這些公司已在國外擁有大量資源儲備

1月19日早間,布倫特原油期貨站上89美元 桶,日內(nèi)漲超1 6%,續(xù)創(chuàng)逾7年新高。日前,阿聯(lián)酋首都阿布扎比...

-

河南19日新增本土確診病例24例

中新經(jīng)緯1月20日電據(jù)河南衛(wèi)健委網(wǎng)站20日消息,1月19日0—24時,全省新增本土確診病例24例(鄭州市1例,安...

-

芝加哥農(nóng)產(chǎn)品期價19日上漲

新華社芝加哥1月19日電(記者徐靜)芝加哥期貨交易所玉米、小麥和大豆期價19日全線上漲。 當天,芝加...

-

電建地產(chǎn)擬發(fā)行不超過10億公司債 詢價區(qū)間3.0%-4.0%

觀點網(wǎng)訊:1月19日,中國電建地產(chǎn)集團有限公司發(fā)布公告稱,擬發(fā)行2022年面向?qū)I(yè)投資者公開發(fā)行公司債券...

-

國際油價19日顯著上漲

新華社紐約1月19日電(記者劉亞南)國際油價19日顯著上漲。 截至當天收盤,紐約商品交易所2月交貨的...

-

大基建潮涌 水泥“雙碳元年”將至

□水泥頭部企業(yè)圍繞“降碳”“降耗”各展所長。 □各地落后產(chǎn)能退出提速,頭部企業(yè)“搶灘”產(chǎn)能勢頭...

-

成都成華舊改2021年新增借款金額60.49億

觀點網(wǎng)訊:1月19日,成都成華舊城改造投資有限責任公司發(fā)布公告稱,2021年公司累計新增借款余額為60 49...

-

美聯(lián)儲收緊路徑與影響:這一次有何不同?

基準情形下,美聯(lián)儲或于5月首次加息,但不排除最早3月加息的可能,全年加息3次,6月或開啟縮表。本輪緊...

-

多部門詳解“十四五”綜合交通運輸發(fā)展重點

在19日召開的國家發(fā)展改革委新聞發(fā)布會上,國家鐵路局、民用航空局、國家郵政局等多部門相關(guān)負責人詳解...

-

格力集團擬發(fā)行10億3年期公司債 利率詢價區(qū)間2.7%-3.7%

觀點網(wǎng)訊:1月19日,據(jù)珠海格力集團有限公司披露,該公司擬發(fā)行2022年面向?qū)I(yè)投資者公開發(fā)行公司債券(...

-

國際油價創(chuàng)七年新高

受地緣政治緊張局勢威脅原油供應等因素的影響,國際油價1月18日升至七年來新高。分析人士指出,面對疫情...

-

微軟收購暴雪:用過去的王炸打前往未來的牌

1月18日晚間,一則并購消息引爆了沉寂已久的游戲圈。據(jù)中國基金報報道,微軟公司發(fā)布聲明稱,將以每股95...

-

美股收盤:三大指數(shù)集體收跌 納指跌超1%

財聯(lián)社(上海,編輯夏軍雄)訊,美東時間周三,美股市場高開低走,延續(xù)了近期的跌勢,三大股指悉數(shù)收跌...

-

十倍杠桿打新港股爆倉!有股民遭平倉虧掉數(shù)百萬,提出富途證券為虧損“買單”,損失究竟誰之過?

十倍杠桿打新港股爆倉!有股民遭平倉虧掉數(shù)百萬,提出富途證券為虧損“買單”,損失究竟誰之過?財聯(lián)社...

-

九部委聯(lián)合發(fā)文規(guī)范平臺企業(yè)投資入股金融機構(gòu)、地方金融組織 對互聯(lián)網(wǎng)巨頭將有何影響?

九部委聯(lián)合發(fā)文規(guī)范平臺企業(yè)投資入股金融機構(gòu)、地方金融組織對互聯(lián)網(wǎng)巨頭將有何影響?財聯(lián)社(北京,記...

-

廣州:對國際快遞收件人員實施常態(tài)化免費核酸檢測

中新經(jīng)緯1月19日電廣州市交通運輸局官方微博19日發(fā)文稱,根據(jù)廣州市疫情防控工作需要,廣州市新冠肺炎防...

-

全球疫情動態(tài)【1月19日】:西安疫情首次“零新增” 疫情已進入收尾階段

財聯(lián)社(上海,編輯夏軍雄)訊,美國約翰斯·霍普金斯大學發(fā)布的統(tǒng)計數(shù)據(jù)顯示,截至北京時間1月19日23時...

-

美國財長耶倫:奧密克戎毒株不會破壞美國經(jīng)濟復蘇

財聯(lián)社(上海,編輯夏軍雄)訊,當?shù)貢r間周三(1月19日),美國財政部長珍妮特·耶倫表示,她預計奧密克...

-

美股全線收跌 中概股叮咚買菜跌近24%

中新經(jīng)緯1月20日電美東時間周三,美股三大指數(shù)高開低走,納指跌超1%。具體來看,截至收盤,道指跌339 8...

-

一線城市暫未出現(xiàn)房貸利率大面積下行 業(yè)內(nèi)人士:靜等明日5年期LPR報價結(jié)果

財聯(lián)社(北京、上海,記者姜樊徐川)訊,財聯(lián)社記者今日從北、上、廣、深等多地的銀行了解到,由于去年...

-

【明日主題前瞻】豪擲近700億美元,微軟加速布局元宇宙游戲領(lǐng)域

【主題詳情】豪擲近700億美元,微軟加速布局元宇宙游戲領(lǐng)域,這些公司已擁有大量游戲IP微軟宣布將以每股...

-

警方通報:山東運泰物流一貨車內(nèi)貨物爆炸 2名裝卸工人受傷

中新經(jīng)緯1月19日電19日,山東省臨沂市公安局蘭山分局官方微博通報稱,1月19日10時34分,蘭山警方接報警...

-

三元生物:八年無新增發(fā)明專利授權(quán) 昔日財務總監(jiān)履歷“玩穿越”

《金證研》北方資本中心易安 作者巫恩歡笙 風控“渤海之濱,黃河之洲”,山東省濱州市因此而得名,并...

-

今年來最大范圍雨雪將至!官方:保證“菜籃子”生產(chǎn)安全

中新經(jīng)緯1月19日電今年來最大范圍雨雪將上線。農(nóng)業(yè)農(nóng)村部表示,把做好雨雪天氣防范工作作為當前農(nóng)業(yè)生產(chǎn)...

-

湯圓怎么挑?寧波市消保委提醒這五點

中新經(jīng)緯1月19日電據(jù)寧波市消保委官方微信消息,1月19日,寧波市消保委對思念、缸鴨狗、灣仔碼頭等10款...

-

大悅城:中糧置業(yè)完成發(fā)行15億元公司債券

焦點財經(jīng)訊耿宸斐1月19日,大悅城(SZ000031)發(fā)布關(guān)于控股子公司中糧置業(yè)投資有限公司2022年公司債券(第...

-

急!這類企業(yè)直接發(fā)現(xiàn)金留人!有員工獎勵達8000元→

全球多地疫情高發(fā),海外確診人數(shù)不斷攀升,對新冠病毒檢測試劑盒的需求激增,這也直接導致國內(nèi)檢測試劑...

-

網(wǎng)信辦辟謠:從未出臺《互聯(lián)網(wǎng)企業(yè)上市及投融資操作規(guī)范》

焦點財經(jīng)訊耿宸斐1月19日,據(jù)“網(wǎng)信中國”公眾號消息,中國網(wǎng)信網(wǎng)關(guān)注到,1月19日網(wǎng)上流傳“中央網(wǎng)信辦...

-

融資丨「C咖」完成B輪融資,SIG領(lǐng)投

創(chuàng)業(yè)邦獲悉,今日,新銳國貨面膜品牌C咖完成B輪融資。本輪融資由SIG領(lǐng)投,老股東順為資本、不二資本、百...

-

國務院聯(lián)合調(diào)查組對中石油燃料油公司倒賣進口原油問題進行嚴肅調(diào)查處理

近期審計署審計發(fā)現(xiàn),中國石油(601857,診股)天然氣集團有限公司下屬燃料油公司存在倒賣進口原油問題。經(jīng)...

-

旭輝一日雙響:美元債資金提前到位,人民幣債券提前回購

1月19日晚間,旭輝控股集團(0884 HK)發(fā)布公告稱,公司已回購并注銷2000萬元今年4月到期,票面利率為6...

-

金融壹賬通獲中國智能科學技術(shù)最高獎

1月19日,經(jīng)過中國人工智能學會專家組數(shù)月的多輪評審,由金融壹賬通牽頭建設(shè)的“普惠金融人工智能開放平...

-

中汽協(xié):2021年12月新能源汽車市場滲透率達19.1%

上證報中國證券網(wǎng)訊據(jù)“中汽協(xié)會數(shù)據(jù)”微信公眾號1月19日消息,據(jù)中國汽車工業(yè)協(xié)會統(tǒng)計分析,2021年新能...

-

中青寶因違反上市公司信披管理辦法遭責令改正 相關(guān)責任人收警示函

中國網(wǎng)科技1月19日訊今日,中青寶(300052,診股)發(fā)布關(guān)于收到中國證監(jiān)會深圳監(jiān)管局對公司采取責令改正措...

-

春節(jié)前全國高速整體平穩(wěn) 2月6日將迎返程高峰

今天(19日)是2022年春運的第三天。交通運輸部預測顯示,今年春運總體將呈現(xiàn)“客流總量中低位運行、節(jié)...

-

突發(fā)!剛通報,北京新增5例陽性,詳情公布!攜程沖上熱搜,上海回應,正開展排查! 2000億巨頭換帥,

突發(fā)!剛通報,北京新增5例陽性,詳情公布!攜程沖上熱搜,上海回應,正開展排查!2000億巨頭換帥,國內(nèi)...

-

央行:涉奧主體賬戶、銀行卡等支付服務籌備工作已就緒

中新經(jīng)緯1月19日電據(jù)中國人民銀行官方微信消息,目前,涉奧主體賬戶、銀行卡、移動支付、本外幣現(xiàn)金、數(shù)...

-

全球最大純電動游輪“長江三峽1”號試航成功

上證報中國證券網(wǎng)訊據(jù)國資委官網(wǎng)“央企聯(lián)播”欄目1月19日消息,近日,全球載電量最大的純電動游輪“長江...

-

京東七鮮超市重點布局大灣區(qū)在廣州越秀開店:匯聚百款京東自有品牌及全球萬款商品

近日,京東七鮮超市越秀區(qū)流花中心店正式開業(yè),這是七鮮在廣州的第五家門店,是越秀區(qū)的首店,也是華南...

-

農(nóng)業(yè)農(nóng)村部:1月19日“農(nóng)產(chǎn)品批發(fā)價格200指數(shù)”比昨天上升0.23個點

上證報中國證券網(wǎng)訊據(jù)農(nóng)業(yè)農(nóng)村部監(jiān)測,1月19日“農(nóng)產(chǎn)品批發(fā)價格200指數(shù)”為128 14,比昨天上升0 23個...

-

國內(nèi)期市日間盤多數(shù)品種收漲 鄭煤主力合約漲逾6%

上證報中國證券網(wǎng)訊1月19日國內(nèi)期市日間盤多數(shù)品種收漲,鄭煤主力合約漲逾6%,鐵礦石、瀝青主力合約漲超...

-

防控不力!北京海淀通報6家單位,肯德基、必勝客在列

中新經(jīng)緯1月19日電19日,據(jù)微信公眾號“北京海淀”消息,因未落實疫情防控責任,海淀區(qū)市場防疫組通報6...

-

上市后首推員工持股計劃 邁瑞醫(yī)療20%業(yè)績增長或成常態(tài)

中新經(jīng)緯1月19日電1月19日,深圳邁瑞生物醫(yī)療電子股份有限公司(以下簡稱“邁瑞醫(yī)療(300760,診股)”“邁...

-

工信部:2021年1-11月規(guī)模以上化纖企業(yè)利潤總額同比增長221.9%

上證報中國證券網(wǎng)訊據(jù)工業(yè)和信息化部消息,2021年1-11月,化纖產(chǎn)量6139萬噸,同比增長10 3%;規(guī)模以上...

-

紅星美凱龍非執(zhí)行董事徐宏因個人工作調(diào)整辭職

焦點財經(jīng)訊耿宸斐1月19日,紅星美凱龍(HK:01528)發(fā)布關(guān)于非執(zhí)行董事辭任的公告。根據(jù)公告,紅星美凱龍于...

-

工信部:2021年1-11月,服裝行業(yè)規(guī)模以上企業(yè)利潤總額同比增長12.6%

上證報中國證券網(wǎng)訊據(jù)工業(yè)和信息化部消息,2021年1-11月,服裝行業(yè)規(guī)模以上企業(yè)12659家,累計營業(yè)收入1...

-

2021年我國全年社會物流總額預計超300萬億元

中國物流與采購聯(lián)合會會長何黎明近日在第十九屆中國物流企業(yè)家年會上介紹說,2021年我國經(jīng)濟整體保持回...

-

警報拉響!2022年首家“1元退市”公司將誕生?另有多家公司觸及財務類退市線

財聯(lián)社1月19日訊,*ST新億(600145 SH)連續(xù)3天跌停,昨日報收0 92元,成為2022年首只跌破1元的個股,18...

-

減負不減責 信息基礎(chǔ)設(shè)施撐腰 監(jiān)管取消涉及保險資金運用的34項監(jiān)管報告

財聯(lián)社(北京,記者王宏)訊,銀保監(jiān)會今日印發(fā)《關(guān)于精簡保險資金運用監(jiān)管報告事項的通知》(以下簡稱...

-

金融“融”進來 蘋果“紅”起來——中投公司發(fā)揮金融優(yōu)勢助力靜寧蘋果產(chǎn)業(yè)振興紀實

上證報中國證券網(wǎng)訊作為深耕全球市場十余年的國家主權(quán)財富基金,中投公司始終心懷“國之大者”,積極履...

-

首次突破8000億!河南外貿(mào)進出口再創(chuàng)歷史新高

記者19日從鄭州海關(guān)了解到,2021年河南外貿(mào)進出口總值達8208 1億元,比2020年增長22 9%(與2019年相比...

-

新冠病毒可通過普通快件傳播?一文解答所有疑點

“郵件陽性”是否意味著郵件將會成為新冠病毒新的傳染源?普通快件傳染給人的可能性有多大?關(guān)于新冠病...

-

茅臺1935官宣定價后暴漲近40%

從經(jīng)銷商處得知,前一日剛宣布定價的茅臺1935的市場價格已經(jīng)漲至1650元 瓶,漲幅近40%,甚至在其他終端...

-

廣西2021年港口貨物吞吐量突破5億噸大關(guān) 同比增長18.64%

19日,記者從廣西港航發(fā)展中心了解到,2021年,廣西港航系統(tǒng)積極融入新發(fā)展格局,以加快交通強區(qū)建設(shè)為...

-

國內(nèi)首次!高海拔重冰區(qū)實現(xiàn)特高壓跨越特高壓放線

1月18日,白鶴灘—江蘇±800千伏特高壓直流輸電線路工程在位于四川省涼山彝族自治州的美姑縣沙洛...

-

融資丨「溪礫科技」完成數(shù)千萬美元Pre-A輪融資,順為資本、云九資本、天圖投資共同投資

融資丨「溪礫科技」完成數(shù)千萬美元Pre-A輪融資,順為資本、云九資本、天圖投資共同投資創(chuàng)業(yè)邦獲悉,今日...

-

華夏幸福已簽署債務重組協(xié)議的債務金額為88.57億元

觀點網(wǎng)迅:1月19日,華夏幸福基業(yè)股份有限公司披露關(guān)于公司債務重組的進展。觀點新媒體了解,華夏幸福在...

-

融資丨「星云有客」連續(xù)完成共四千萬元天使輪及Pre-A輪融資

創(chuàng)業(yè)邦獲悉,今日,杭州星云數(shù)字科技有限公司提升。初心資本管理合伙人田江川表示:“從消費者互動側(cè)來...

-

融創(chuàng)相繼轉(zhuǎn)讓三個項目公司股權(quán) 接盤方均有國企背景

中新經(jīng)緯1月19日電(薛宇飛)近日,中新經(jīng)緯查詢工商信息發(fā)現(xiàn),融創(chuàng)在近段時間相繼轉(zhuǎn)讓了至少3家項目公司...

-

金融“融”進來 蘋果“紅”起來——中投公司發(fā)揮金融優(yōu)勢助力靜寧蘋果產(chǎn)業(yè)振興紀實

上證報中國證券網(wǎng)訊作為深耕全球市場十余年的國家主權(quán)財富基金,中投公司始終心懷“國之大者”,積極履...

-

國常會:決定延續(xù)實施部分到期的減稅降費政策 支持企業(yè)紓困和發(fā)展

李克強主持召開國務院常務會議。會議指出,決定延續(xù)實施部分到期的減稅降費政策,支持企業(yè)紓困和發(fā)展。...

-

安徽滁州3.1億掛牌1宗商住地 將于2月18日出讓

觀點網(wǎng)訊:1月19日,安徽滁州來安縣掛牌1宗商住地,土地面積66472㎡,掛牌起始價31000萬元,預計2月18日...

-

筑友智造:2021年銷售合同額增至46.69億元 產(chǎn)量增加40%

觀點網(wǎng)訊:筑友智造科技集團有限公司1月19日刊發(fā)自愿公告,表示公司預制裝配式建筑構(gòu)件及產(chǎn)品的產(chǎn)量、銷...

-

國務院發(fā)布促進內(nèi)外貿(mào)一體化發(fā)展意見 鼓勵商貿(mào)、物流“走出去”

觀點網(wǎng)訊:1月19日,國務院辦公廳發(fā)布《關(guān)于促進內(nèi)外貿(mào)一體化發(fā)展的意見》。其中提到,支持市場主體內(nèi)外...

-

能源局:2021年國家財政補貼規(guī)模戶用光伏項目裝機容量為2159.62萬千瓦

國家能源局數(shù)據(jù)顯示,2021年12月新納入國家財政補貼規(guī)模戶用光伏項目總裝機容量為508 98萬千瓦。截至20...

-

雅生活服務:股東共青城投資購買合計12萬股境外上市股份

觀點網(wǎng)訊:1月19日,雅生活智慧城市服務股份有限公司發(fā)布公告稱,股東增持股權(quán),共青城投資購買合計12萬...

-

保險機構(gòu)網(wǎng)點緣何驟減?

曾幾何時,“機構(gòu)開到哪里,業(yè)務就做到哪里”是保險行業(yè)最真實的寫照。但是多年的“圈地運動”在2021年...

-

百家名企看高質(zhì)量|百信銀行行長李如東:金融科技引領(lǐng)未來銀行新范式

中新經(jīng)緯1月19日電(魏薇實習生柴鑫洋)“未來的銀行,要順應數(shù)字經(jīng)濟的大趨勢,持續(xù)進行數(shù)字化的探索和迭...

-

2021年我國全年社會物流總額預計超300萬億元

中國物流與采購聯(lián)合會會長何黎明近日在第十九屆中國物流企業(yè)家年會上介紹說,2021年我國經(jīng)濟整體保持回...

-

《可信人工智能白皮書》被全球頂級智庫列為中國人工智能治理三大方法之一

切實推進人工智能治理工作,已成為全球共識。近日,由京東探索研究院與中國信通院聯(lián)合撰寫的國內(nèi)首本《...

-

陳茂波指對再發(fā)放消費券目前會持開放態(tài)度

觀點網(wǎng)訊:1月19日,香港財政司長陳茂波表示,電子消費券已分批向合資格市民發(fā)放共300億港元,對經(jīng)濟復...

-

護膚品牌「C咖」獲SIG投資 旗下清潔小罐膜位居抖音面膜類目Top1

金融界1月19日消息,近日,新銳護膚品牌「C咖」完成由SIG領(lǐng)投的B輪融資,老股東順為資本、不二資本、百...